В мире

Техпроцессы меньше 1 нанометра ждать до 2034 года: дорожная карта IMEC

Техпроцессы меньше 1 нанометра появятся только к 2034 году — новый прогноз IMEC

Автор: Александр Кондратьев

04 мая 2026

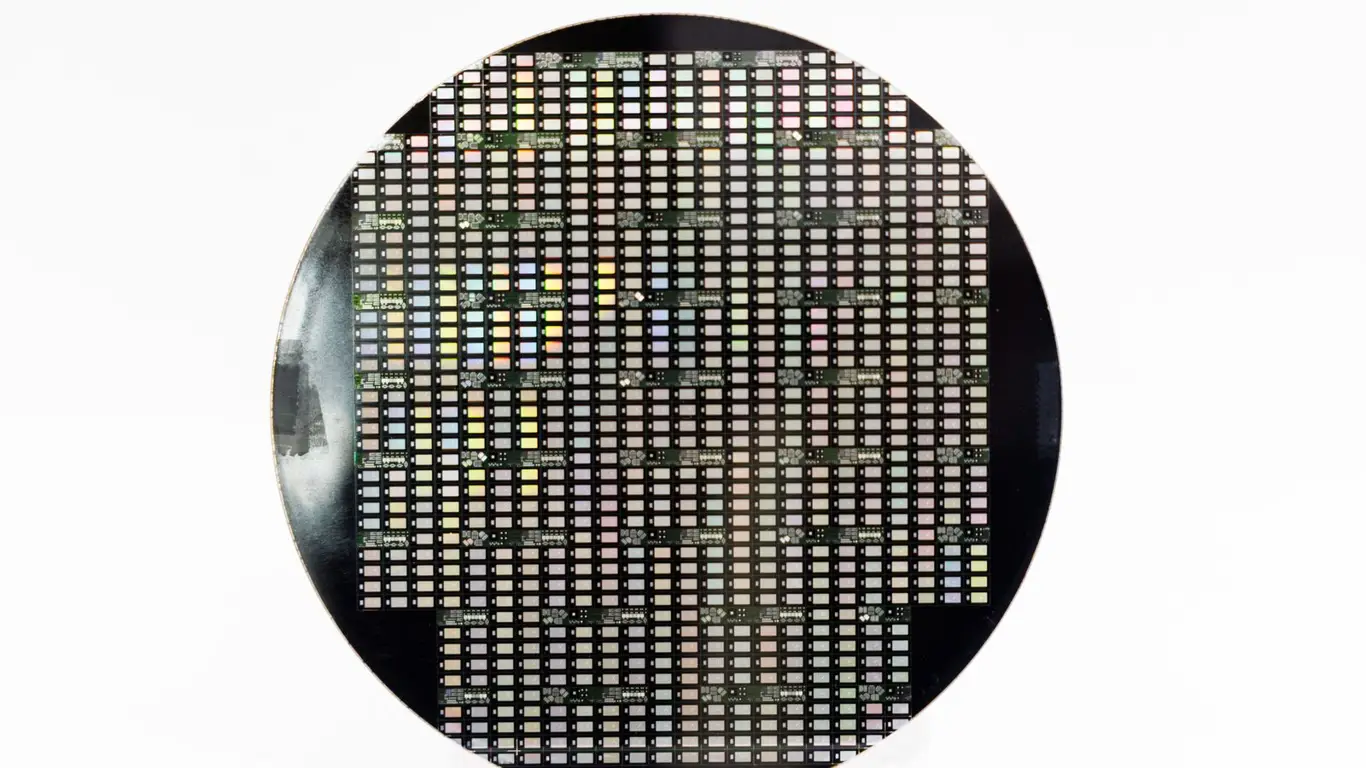

Фото: © D. Novikov

Переход к техпроцессам с нормами менее 1 нанометра произойдет не раньше 2034 года, согласно обновленной дорожной карте исследовательского центра IMEC. В документе описывается эволюция логических чипов с 2020-х по 2040-е годы, отмечается, что закон Мура продолжает работать, но его темпы значительно замедлились. В ближайшей перспективе акцент делается на многослойных Gate-All-Around транзисторах, а первым значимым шагом станет 2-нм техпроцесс N2, после чего появятся разработки ангстремного уровня, такие как A14 и A10. pepelac.news

IMEC уточняет, что представленные даты относятся не к выпуску готовой продукции, а к завершению разработки новых технологий. Этапа A7 (0,7 нм) ожидают следующим после A10, затем к 2036 году планируется A5, а к 2040-му — A3. Ключевой архитектурой для суб-нанометровых узлов станут CFET-транзисторы, где p- и n-каналы расположены вертикально друг над другом.

В 2040-х годах отрасль, вероятно, начнет использовать 2D FET-транзисторы из новых материалов. По прогнозу, к 2043 году они лягут в основу узла A2 (0,2 нм), а к 2046 году возможно снижение норм ниже 0,2 нм. Однако эти оценки остаются исследовательскими и могут корректироваться.

IMEC подчеркивает, что только совершенствования транзисторов недостаточно: развитие ИИ-ускорителей, HPC-систем и будущих процессоров потребует прогресса в 2,5D- и 3D-упаковке, чиплетах, новых межсоединениях, интегрированных регуляторах напряжения и эффективных схемах питания.